Уроки 54 - 55

Логические основы устройства компьютера

§ 3.2. Логические основы устройства компьютера

Содержание урока

3.2.1. Базовые логические элементы

3.2.2. Сумматор двоичных чисел

3.2.2. Сумматор двоичных чисел

В целях максимального упрощения работы компьютера всё многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора является сумматор, который как раз и обеспечивает такое сложение. Сумматор составляется из базовых логических элементов.

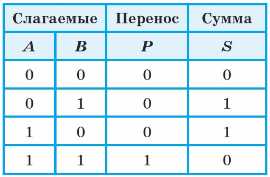

Полусумматор. При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд. Обозначим слагаемые — А и В, перенос — Р и сумму — S. Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом (табл. 3.4).

Полусумматор. При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд. Обозначим слагаемые — А и В, перенос — Р и сумму — S. Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом (табл. 3.4).

Таблица 3.4. Таблица сложения одноразрядных двоичных чисел

Из этой таблицы видно, что перенос можно реализовать с помощью операции логического умножения:

Р = А & В.

Получим теперь формулу для вычисления суммы. Значения суммы более всего совпадают с результатом операции логического сложения (кроме случая, когда на входы подаются две единицы, а на выходе должен получиться ноль).

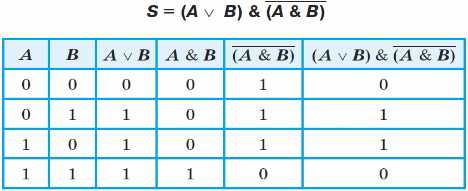

Нужный результат достигается, если результат логического сложения умножить на инвертированный перенос. Таким образом, для определения суммы можно применить следующую логическую функцию:

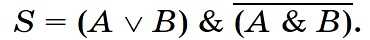

Построим таблицу истинности для данной логической функции и убедимся в правильности нашего предположения (табл. 3.5).

Таблица 3.5. Таблица истинности логической функции

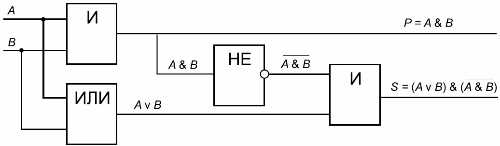

Теперь на основе полученных логических формул можно построить из базовых логических элементов схему сложения одноразрядных двоичных чисел.

По логической формуле переноса можно определить, что для получения переноса необходимо использовать логический элемент «И».

Анализ логической формулы для суммы показывает, что на выходе должен стоять элемент логического умножения «И», который имеет два входа. На один из входов подается результат логического сложения исходных величин A v В, т. е. на него должен подаваться сигнал с элемента логического сложения «ИЛИ».

На второй вход требуется подать результат инвертированного логического умножения исходных сигналов  , т. е. на второй вход подается сигнал с элемента «НЕ», на вход которого поступает сигнал с элемента логического умножения «И» (рис. 3.7).

, т. е. на второй вход подается сигнал с элемента «НЕ», на вход которого поступает сигнал с элемента логического умножения «И» (рис. 3.7).

Данная схема называется полусумматором, так как реализует суммирование одноразрядных двоичных чисел А и В без учета переноса из младшего разряда.

Рис. 3.7. Полусумматор двоичных чисел

Для сложения многоразрядных двоичных чисел служит сумматор, который составляется из полусумматоров.

Контрольные вопросы

1. Какие значения будут иметь перенос и сумма при суммировании одноразрядных двоичных чисел, равных 1, и переноса из младшего разряда?