Уроки 22 - 26

§1.8. Модели логических устройств

Содержание урока

1.8.1. Логические схемы полусумматора и триггера

Триггер

1.8.2. Модели логических устройств компьютера на языке Visual Basic

1.8.3. Модели логических устройств компьютера на языке Turbo Delphi

1.8.4. Модели логических устройств компьютера в электронных таблицах

1.8.1. Логические схемы полусумматора и триггера

Триггер

Триггер. Оперативная память компьютера, а также внутренних регистров процессора состоит из ячеек, которые технически реализуются с помощью триггеров. Триггер — это устройство, которое позволяет записывать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации).

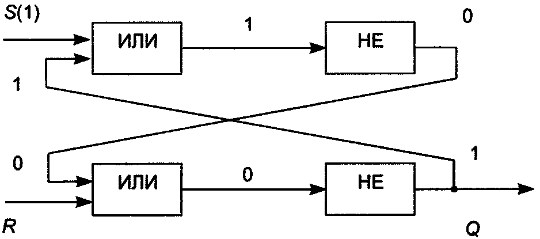

Триггер можно построить из двух логических элементов ИЛИ и двух элементов НЕ (рис. 1.40).

Рис. 1.40. Логическая схема триггера

В обычном состоянии на входы триггера подан сигнал 0, и триггер хранит 0. Для записи 1 на вход S (установочный) подается сигнал 1. Последовательно рассмотрев прохождение сигнала по схеме, увидим, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил 1, т. е. с выхода триггера Q можно считать 1.

Для того чтобы сбросить информацию и подготовиться к приему новой информации, подается сигнал 1 на вход R (сброс), после чего триггер возвратится к исходному «нулевому» состоянию.

Следующая страница  Контрольные вопросы

Контрольные вопросы