Уроки 27 - 30

Предикаты и кванторы. Логические элементы компьютера. Логические задачи

§23. Предикаты и кванторы. §24. Логические элементы компьютера. §25. Логические задачи

Содержание урока

§23. Предикаты и кванторы

§24. Логические элементы компьютера

Триггер

§25. Логические задачи

§24. Логические элементы компьютера

Триггер

Слово «триггер» происходит от английского слова «trigger» — «защёлка» или спусковой крючок 1. Так называют электронную схему, которая может находиться только в двух состояниях (их можно обозначить как 0 и 1) и способна почти мгновенно переходить из одного состояния в другое. Триггер изобрели независимо друг от друга М. А. Бонч-Бруевич и англичане У. Икклз и Ф. Джордан в 1918 г.

1 В английском языке триггер называется flip-flop.

В современных компьютерах на основе триггеров строится быстродействующая оперативная память. Один триггер способен хранить один бит данных. Соответственно, для того, чтобы запомнить 1 байт информации, требуется 8 триггеров, а для хранения 1 килобайта данных — 8 • 1024 = 8192 триггера.

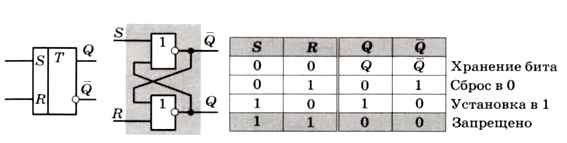

Триггеры бывают разных типов. Самый распространённый — это RS-триггер. Он имеет два входа, которые обозначаются как S (англ, set — установить) и R (англ, reset — сброс), и два выхода — Q и Q, причём выходной сигнал Q является логическим отрицанием сигнала Q (если Q = 1, то Q = 0, и наоборот).

RS-триггер можно построить на двух элементах «И-НЕ» или на двух элементах «ИЛИ-HE». На рисунке 3.26 показано условное обозначение RS-триггера, внутреннее устройство триггера на элементах «ИЛИ-HE» и его таблица истинности.

Рис. 3.26

Триггер использует так называемые обратные связи — сигналы с выходов схем «ИЛИ-HE» поступают на вход соседней схемы. Именно это позволяет хранить информацию.

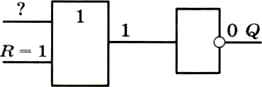

Построим таблицу истинности триггера. Начнем с варианта, когда S = 0 и R = 1. Элемент «ИЛИ-HE» в нижней части схемы можно заменить на последовательное соединение элементов «ИЛИ» и «НЕ». Независимо от второго входа, на выходе «ИЛИ» будет 1, а на выходе «НЕ» — ноль. Это значит, что Q = 0 (рис. 3.27).

Рис. 3.27

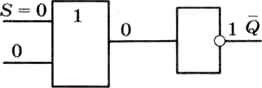

Тогда на входе другого элемента «ИЛИ-HE» будут два нуля, а на выходе Q — единица (рис. 3.28).

Рис. 3.28

Поскольку основным выходом считается Q, мы записали в триггер значение 0. Схема симметрична, поэтому легко догадаться, что при S = 1 и R = 0 мы запишем в триггер 1 (Q = 1).

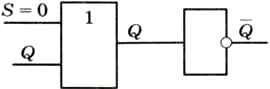

Теперь рассмотрим случай, когда S = 0 и R = 0. На входе первого элемента «ИЛИ» будет сигнал Q + 0 = Q, поэтому на выходе Q останется его предыдущее значение (рис. 3.29).

Рис. 3.29

Аналогично легко показать, что на выходе Q тоже остаётся его предыдущее значение. Это режим хранения бита.

Для случая S = 1 и R = 1 мы увидим, что оба выхода становятся равны нулю — в этом нет смысла, поэтому такой вариант запрещён.

Для хранения многоразрядных данных триггеры объединяются в единый блок, который называется регистром. Регистры (размером от 8 до 64 битов) используются во всех процессорах для временного хранения промежуточных результатов.

Над регистром, как над единым целым, можно производить ряд стандартных операций: сбрасывать (обнулять), заносить в него код и т. д. Часто регистры способны не просто хранить информацию, но и обрабатывать её. Например, существуют регистры- счётчики, которые подсчитывают количество импульсов, поступающих на вход.

Следующая страница  Сумматор

Сумматор